# VLSI-design of reconfigurable logic blockbased sequential circuits using Look-up table logics

G.Devika<sup>1</sup>, E.Thrishika<sup>2</sup>, K.Harshasree<sup>3</sup>, Mr.Venkanna Mood<sup>4</sup>

<sup>1,2,3</sup>UG Scholar, Dept. of ECE, St. Martin's Engineering College, Secunderabad, Telangana, India-500100 <sup>4</sup>Associate Professor, Dept. of ECE, St. Martin's Engineering College, Secunderabad, Telangana, India-500100

gundojidevika@gmail.com

#### Abstract:

The advancement of Very-Large-Scale Integration (VLSI) technology has made it possible to create highly efficient sequential circuits, such as counters and shift registers, utilizing reconfigurable logic blocks. Statistics show that by 2026, the global VLSI market is projected to reach approximately \$50 billion, driven by the demand for versatile and adaptive electronic components in various applications. Traditional logic gate-based sequential circuits often suffer from inflexibility and high resource consumption, leading to inefficiencies in design and performance, particularly in dynamic environments where rapid reconfiguration is required.

This paper proposes a novel approach to designing sequential circuits based on reconfigurable logic blocks using lookup table (LUT) logic. By employing LUT-based architectures, the proposed counters and shift registers achieve greater adaptability and lower power consumption compared to conventional designs. The utilization of LUTs allows for efficient implementation of complex logic functions while simplifying the overall design process. This innovation not only enhances performance metrics such as speed and power efficiency but also facilitates faster prototyping and testing in VLSI front-end design. The resulting reconfigurable logic blocks offer a significant contribution to the design landscape, making it easier to meet the diverse requirements of modern electronic applications.

Keywords: VLSI design, LUT-based architecture Reconfigurable circuits, Sequential logic design Low-power circuits, High-speed design Logic optimization, Digital circuit prototyping Adaptive electronics, FPGA-based design

#### 1. INTRODUCTION

Sequential circuits are digital circuits that store and use the previous state information to determine their next state. Unlike combinational circuits, which only depend on the current input values to produce outputs, sequential circuits depend on both the current inputs and the previous state stored in memory elements. Sequential circuits are commonly used in digital systems to implement state machines, timers, counters, and memory elements. The memory elements in sequential circuits can be implemented using flip-flops, which are circuits that store binary values and maintain their state even when the inputs change. There are two types of sequential circuits: Asynchronous and Synchronous sequential circuits.

Asynchronous Sequential Circuit: These circuits do not use a clock signal but uses the pulses of the inputs as shown in Figure 1.1. These circuits are faster than synchronous sequential circuits because there is clock pulse and change their state immediately when there is a change in the input signal. We use asynchronous sequential circuits when speed of operation is important and independent of internal clock pulse. But these circuits are more difficult to design and their output is uncertain.

Figure: 1.1 Asynchronous Sequential Circuit

**Synchronous Sequential Circuit:** These circuits **use clock signal** and level inputs (or pulsed) (with restrictions on pulse width and circuit propagation) as shown in Figure 1.2. The output pulse is the same duration as the clock pulse for the clocked sequential circuits. Since they wait for the next clock pulse to arrive to perform the next operation, so these circuits are bit **slower** compared to asynchronous. Level output changes state at the start of an input pulse and remains in that until the next input or clock pulse.

Figure: 1.2 Synchronous Sequential Circuit

#### **1.2 Research Motivation**

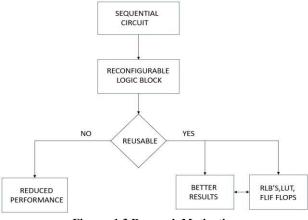

Figure 3.1 shows the reconfigurable logic block based sequential circuit. In this block diagram the first block contains sequential circuits are a type of digital circuit in which the output depends not only on the current inputs but also on the past sequence of inputs. These circuits have memory elements, typically in the form of flip-flops, to store information about previous inputs and outputs.

**Figure: 1.3 Research Motivation**

The preceding block mentions that the reconfigurable logic blocks are programmable, adaptable, and dynamic in nature. These blocks are fundamental components in reconfigurable devices, such as

# ISSN NO: 9726-001X

Volume 13 Issue 02 2025

Field-Programmable Gate Arrays (FPGAs). These blocks provide a level of flexibility and programmability that allows users to configure the hardware for specific tasks or applications. If the reconfigurable logic block incorporates reusability, the system performance is enhanced; otherwise, the absence of this property may lead to a decline in performance.

## 2. LITERATURE SURVEY

[1] Sanadhya, et al. developed a power optimization method for battery-powered digital circuits using adiabatic logic. This approach reduces power dissipation by slowing logic transitions and improving energy efficiency in VLSI circuits. Various adiabatic techniques were analyzed for combinational and sequential circuits, showing better performance than traditional methods.

[2] Govindaraj, et al. proposed a low-power test pattern generator (TPG) using LFSR and binary ripple counter to minimize dynamic power consumption during VLSI circuit testing. Their approach increased the correlation between successive test vectors, significantly reducing power dissipation in test mode.

[3] **Pomeranz, et al.** suggested an iterative synthesis method to improve VLSI design parameters and detect undetectable faults efficiently. Their approach prevents a decrease in fault coverage by identifying and eliminating ineffective design modifications in test generation.

[4] Angadi, et al. developed a built-in self-test (BIST) architecture for combinational logic circuit verification. Using LFSR-based test patterns, the proposed method effectively detects errors in circuits

[10] Ramakrishnan, et al. explored reversible logic for low-power combinational and sequential circuits. Their MGDI-based approach minimizes power consumption, transistor count, and propagation delay while maintaining logic simplicity, enhancing VLSI circuit design.

[11] Harikrishna, et al. designed a low-power square root calculator using reversible logic and a non-restoring algorithm. The binary square rooter, implemented using RCSM and SRG gates, reduces hardware resources while maintaining efficient power consumption.

**[12]** Nousheen, et al. proposed a hardware-oriented image compression algorithm for wireless sensor networks. Their approach integrates fuzzy decision-making, block partitioning, and Huffman coding, achieving high compression ratios while maintaining low power consumption.

[13] Geonhwi, et al. developed a high-speed, low-power synchronous up/down counter using a compact toggle flip-flop. Their design improves counting speed by 55% and reduces power-delay product by 28%, enhancing energy-efficient VLSI designs.

**[14] Moraitis, et al.** surveyed FPGA security threats and bitstream modification attacks. They discussed existing protection mechanisms, potential vulnerabilities, and countermeasures to ensure FPGA-based systems' security in critical applications.

[15] Irith, et al. introduced a test data compression method for scanbased testing, reducing test sequence length. Their approach enables efficient on-chip decompression, minimizing test data storage requirements while maintaining fault coverage.

while minimizing hardware complexity, making testing more efficient and cost-effective.

[5] Chandra, et al. focused on low-power VLSI design strategies, particularly optimizing adders for better power and area efficiency. They proposed a ripple carry adder using full swing gate diffusion input technology to reduce size, power, and complexity in digital circuits.

**[6] Priyadarshini, et al.** designed a novel D Flip Flop (DFF) using supply voltage techniques to lower leakage power consumption. Their method reduces power dissipation in standby mode while employing fewer transistors, improving efficiency in CMOS-based digital designs.

[7] Minakshi, et al. proposed a D Flip Flop using direct current diode-based positive feedback adiabatic logic (DC-DB PFAL) to reduce power dissipation. Their analysis at various frequencies showed an 18% improvement in power efficiency with fewer transistors than existing designs.

[8] Shah, et al. introduced a sense amplifier-based flip flop (SAFF) for high-speed and low-power applications. The proposed flip flop achieves significant power reduction, glitch-free operation, and improved speed, making it suitable for high-performance VLSI circuits.

[9] Yinghua, et al. developed an FC-guided SAT-based attack to break combinational and sequential logic locking efficiently. Their approach significantly speeds up key retrieval in logic encryption, reducing SAT-solving time by up to  $90\times$  compared to previous attacks.

# 3. PROPOSED METHODOLOGY

Counters in digital circuits are fundamental components used to generate sequences of binary numbers. They are widely employed in various applications such as frequency division, digital clocks, event counting, and addressing memory locations. Counters can be synchronous or asynchronous and come in different types such as binary counters, BCD (Binary-Coded Decimal) counters, and asynchronous counters. In VLSI, counters are digital circuits used to count events or sequences of events. They are widely used in various applications such as frequency synthesis, digital signal processing, and timing generation. Counters can be classified based on their type (e.g., binary, BCD, asynchronous, synchronous), counting direction (up or down), and triggering mechanism (e.g., synchronous or asynchronous).

#### **Types of Shift Registers**

- Serial-in Serial-out (SISO): Data is entered serially at one end and shifted out serially at the other end.

- Serial-in Parallel-out (SIPO): Data is entered serially and output in parallel.

- Parallel-in Serial-out (PISO): Data is entered in parallel and shifted out serially.

- Parallel-in Parallel-out (PIPO): Data is entered and output in parallel.

Shift registers in VLSI refer to the implementation of shift registers using integrated circuit technology, typically using CMOS (Complementary Metal-Oxide-Semiconductor) fabrication processes. In VLSI design, shift registers are often optimized for ISSN NO: 9726-001X

# Volume 13 Issue 02 2025

area, speed, and power efficiency to meet the requirements of modern digital systems. Overall, shift registers play a crucial role in VLSI design, enabling the implementation of various digital functionalities in modern integrated circuits.

#### **Proposed Counter**

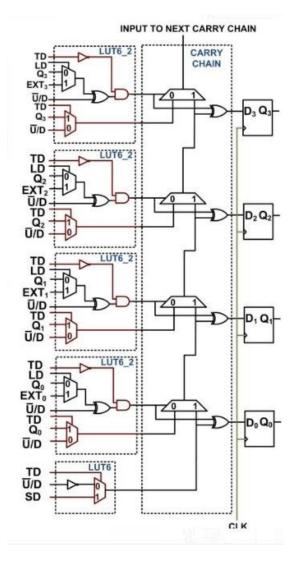

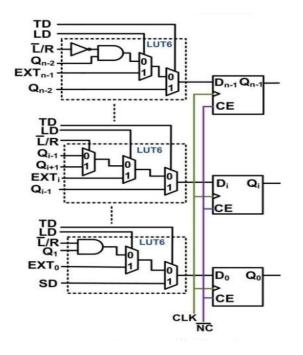

The above figure 4.1 shows proposed architecture for scan FF inserted bidirectional counters.

Figure: 4.1 proposed architecture for scan FF inserted bidirectional counters

#### LUT

In VLSI, a LUT (Look-Up Table) is a fundamental component used in digital logic design. It's essentially a small, programmable memory unit that stores output values for all possible input combinations. LUTs are commonly used in FPGA (Field-Programmable Gate Array) designs to implement logic functions and to perform tasks such as signal processing, arithmetic operations, and data manipulation. They provide flexibility and efficiency in implementing complex logic functions by allowing designers to define custom logic without the need for dedicated hardware.

# JOURNAL OF

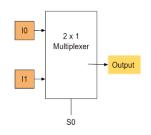

2-to-1 multiplexer

A 2-to-1 multiplexer (mux) is a fundamental component in digital circuits that selects between two input signals based on a control signal. Its operation is crucial for data selection and routing in various electronic devices, ranging from simple integrated circuits to complex computer systems. Let's delve into the detailed operation of a 2-to-1 multiplexer.

Figure 4.2. Multiplexer 2\*1

| Inpu | its | SO | Output |

|------|-----|----|--------|

| 10   | I1  |    |        |

| 0    | 0   | 0  | 0      |

| 0    | 1   | 0  | 1      |

| 1    | 0   | 1  | 1      |

| 1    | 1   | 1  | 1      |

Table 4.2. Multiplexer 2\*1

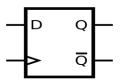

Figure 4.3. D-Flip Flop Without CE

| D | Q | ¯Q |

|---|---|----|

| 0 | Q | 0  |

| 1 | Q | 1  |

Table 4.3. D-Flip Flop Without CE

## ISSN NO: 9726-001X

# Volume 13 Issue 02 2025

# **Proposed Shift registers**

#### Figure 4.4. Proposed architecture for scan FF inserted Universal Shift Register

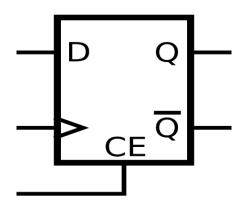

# **D-Flip Flop With CE**

A D flip-flop with a clock enable (CE) input is a digital storage device that holds one bit of data. In addition to the data input (D), it features a clock enable input (CE) which determines when the flip-flop is allowed to change its state. When the clock enable signal is high, the flip-flop operates as normal, capturing the input data on the rising or falling edge of the clock signal.

Figure 4.3. D-Flip Flop With CE

| D | CLK | СЕ | Q | ¯Q |

|---|-----|----|---|----|

| 0 | 1   | 0  | Q | Q  |

| 1 | 1   | 0  | Q | Q  |

| 0 | 1   | 1  | Q | 0  |

| 1 | 1   | 1  | Q | 1  |

# Table 4.3. D- Flip Flop With CE

# 4. EXPERIMENTAL ANALYSIS.

**Existing Counter**

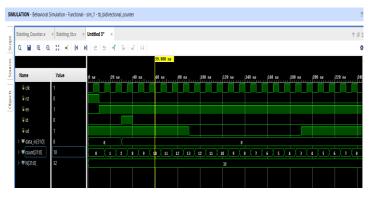

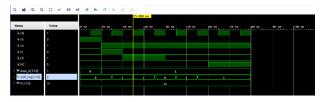

Figure 6.1. Existing Simulation Results for N=32

Figure 6.2 shows existing area measurements for N=32. Here, 1286 number of LUT's are used out of Available 133800 LUT's which consumes 0.96% of utilization, 32 number of FF's are used out of Available 267600 FF's which consumes 0.01% of utilization, 6 number of DSP's are used out of Available 740 DSP's which consumes 0.81% of utilization, 69 number of IO's are used out of Available 500 IO's which consumes 13.80% of utilization, 1 number of BUFG's are used out of Available 32 BUFG's which consumes 3.13% of utilization

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 1286        | 133800    | 0.96          |

| FF       | 32          | 267600    | 0.01          |

| DSP      | 6           | 740       | 0.81          |

| ю        | 69          | 500       | 13.80         |

| BUFG     | 1           | 32        | 3.13          |

#### Figure 6.2. Existing Area for N=32

Figure 6.3 shows existing Setup delay for N=32. Here, maximum Total Delay is 113.892 ns, maximum Logic Delay is 58.494 ns, maximum Net Delay is 55.397 ns.

| Q –       | ♦ 1                                     | m   •  | Uncons | trained Paths - | NONE - NONE - Setup  |                |

|-----------|-----------------------------------------|--------|--------|-----------------|----------------------|----------------|

| Name      | Slack ^1                                | Levels | Routes | High Fanout     | From                 | То             |

| Ъ Path 1  | 00                                      | 206    | 174    | 62              | next_count1_reg[1]/C | next_count1_re |

| Ъ Path 2  | 00                                      | 197    | 166    | 62              | next_count1_reg[1]/C | next_count1_re |

| 🤸 Path 3  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 188    | 158    | 62              | next_count1_reg[1]/C | next_count1_re |

| Ъ Path 4  | 00                                      | 179    | 150    | 62              | next_count1_reg[1]/C | next_count1_re |

| 3 Path 5  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 170    | 142    | 62              | next_count1_reg[1]/C | next_count1_re |

| 🤸 Path 6  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 161    | 134    | 60              | next_count1_reg[1]/C | next_count1_re |

| Ъ Path 7  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 152    | 126    | 58              | next_count1_reg[1]/C | next_count1_re |

| 3 Path 8  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 143    | 118    | 56              | next_count1_reg[1]/C | next_count1_re |

| Ъ Path 9  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 134    | 110    | 54              | next_count1_reg[1]/C | next_count1_re |

| Ъ Path 10 | 00                                      | 126    | 103    | 52              | next_count1_reg[1]/C | next_count1_re |

#### Figure 6.3 Existing Setup Delay for N=32

Figure 6.4 shows existing Hold delay for N=32. Here, maximum Total Delay is 1.107 ns, maximum Logic Delay is 0.664 ns, maximum Net Delay is 0.596 ns.

#### Q 😑 😫 🚸 🕅 🔍 Unconstrained Paths - NONE - Hold

| Name      | Slack ^1 | Levels | Routes | High Fanout | From                  | To                    | Total Delay | Logic Delay | Net Delay | Requirement | Source Clock |

|-----------|----------|--------|--------|-------------|-----------------------|-----------------------|-------------|-------------|-----------|-------------|--------------|

| 🕨 Path 11 | œ        | 2      | 1      | 5           | next_count1_reg[0]/C  | next_count1_reg[0]/D  | 0.488       | 0.255       | 0.233     | -00         |              |

| 🕨 Path 12 |          | 4      | 2      | 4           | next_count1_reg[5]/C  | next_count1_reg[6]/D  | 0.911       | 0.531       | 0.380     | -00         |              |

| 🕨 Path 13 | 00       | 4      | 2      | 4           | next_count1_reg[4]/C  | next_count1_reg[4]/D  | 0.943       | 0.487       | 0.456     | -00         |              |

| 🔓 Path 14 | 00       | 4      | 2      | 4           | next_count1_reg[5]/C  | next_count1_reg[8]/D  | 0.953       | 0.616       | 0.337     | -00         |              |

| 🕨 Path 15 | œ        | 4      | 2      | 4           | next_count1_reg[5]/C  | next_count1_reg[5]/D  | 0.984       | 0.487       | 0.497     | -00         |              |

| Ъ Path 16 |          | 3      | 2      | 4           | next_count1_reg[2]/C  | next_count1_reg[3]/D  | 1.034       | 0.559       | 0.475     | -00         |              |

| 🕨 Path 17 | 00       | 3      | 2      | 4           | next_count1_reg[30]/C | next_count1_reg[31]/D | 1.056       | 0.533       | 0.523     | -00         |              |

| 🕨 Path 18 | 00       | 4      | 2      | 4           | next_count1_reg[22]/C | next_count1_reg[22]/D | 1.072       | 0.476       | 0.596     | -00         |              |

| 🕨 Path 19 | 00       | 5      | 3      | 4           | next_count1_reg[5]/C  | next_count1_reg[9]/D  | 1.075       | 0.664       | 0.411     | -00         |              |

| 🕨 Path 20 | 00       | 4      | 2      | 4           | next_count1_reg[17]/C | next_count1_reg[20]/D | 1.107       | 0.616       | 0.491     | -00         |              |

Figure 6.4 Existing Hold Delay for N=32

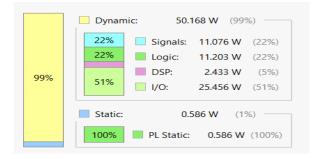

Figure 6.5 shows existing power measurements for N=32. Here, the total power is 50.754 W, Static power includes PL Static power of 0.586 W, Dynamic power includes signal power of 11.076 W, Logic power of 11.203 W, DSP power of 2.433 and I/O power of 25.456 W.

Figure 6.5 Existing power for N=32

Figure 6.6 Proposed Counter Results for N=32

Figure 6.7 shows proposed area measurements for N=32. Here, 32 number of LUT's are used out of Available 133800 LUT's which consumes 0.02% of utilization, 32 number of FF's are used out of Available 267600 FF's which consumes 0.01% of utilization, 69 number of IO's are used out of Available 500 IO's which consumes 13.80% of utilization, 1 number of BUFG's are used out of Available 32 BUFG's which consumes 3.13% of utilization.

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 32          | 133800    | 0.02          |

| FF       | 32          | 267600    | 0.01          |

| ю        | 69          | 500       | 13.80         |

| BUFG     | 1           | 32        | 3.13          |

Figure 6.7 Existing Area for N=32

Figure 6.8 shows proposed Setup delay for N=32. Here, maximum Total Delay is 12.185 ns, maximum Logic Delay is 3.439 ns, maximum Net Delay is 8.754 ns.

| same    | Slack ^1 | Levels. | Routes | High Fanout | From                | To        | Total Delay | Logic Delay | Net Delay | Requirement | Source Clock |

|---------|----------|---------|--------|-------------|---------------------|-----------|-------------|-------------|-----------|-------------|--------------|

| Path 1  | 00       | 2       | 1      | 2           | count_reg_reg[13]/C | count[13] | 12,185      | 3.439       | 8.747     | 60          |              |

| Path 2  | 00       | 2       | 1      | 2           | count_reg_reg[8]/C  | count[8]  | 12.164      | 3.410       | 8.754     | 00          |              |

| Path 3  | .00      | 2       | 1      | 2           | count_reg_reg[14]/C | count[14] | 12.080      | 3.433       | 8.647     | 00          |              |

| Path 4  | -00      | S       | 1      | 2           | count_reg_reg[6]/C  | count[6]  | 12.065      | 3.412       | 8.654     | 03          |              |

| Path 5  |          | 2       | 1      | 2           | count_reg_reg[2]/C  | count[2]  | 12.022      | 3.404       | 8.618     | 60          |              |

| Path 6  |          | 2       | 1      | 2           | count_reg_reg[12]/C | count[12] | 12.015      | 3.397       | 8.619     |             |              |

| Path 7  | 100      | 2       | 1      | 2           | count_reg_reg[5]/C  | count[5]  | 11.990      | 3.404       | 8.585     |             |              |

| Path 8  |          | 2       | 1      | 2           | count_reg_reg[10]/C | count[10] | 11.986      | 3.414       | 8.572     |             |              |

| Path 9  | 60       | 2       | 1      | 2           | count_reg_reg[4]/C  | count[4]  | 11.963      | 3.392       | 8.571     | 60          |              |

| Path 10 | 100      | 2       | 1      | 2           | count reg reg/91/C  | count[9]  | 11.920      | 3,417       | 8,503     |             |              |

#### Figure 6.8 Proposed Setup Delay for N=32

Figure 6.9 shows proposed Hold delay for N=32. Here, maximum Total Delay is 0.599 ns, maximum Logic Delay is 0.349 ns, maximum Net Delay is 0.250 ns.

| Name       | Slack ^1 | Levels | Routes | High Fanout | From                | To                  | Total Delay | Logic Delay | Net Delay | Requirement | Source Cloc |

|------------|----------|--------|--------|-------------|---------------------|---------------------|-------------|-------------|-----------|-------------|-------------|

| - Path 11  | 60       | 3      | 1      | 2           | count_reg_reg[10]/C | count_reg_reg[10]/D | 0.555       | 0.346       | 0.209     | -00         |             |

| la Path 12 | 60       | 3      | 1      | 2           | count_reg_reg[11]/C | count_reg_reg[11]/D | 0.590       | 0.345       | 0.245     | -00         |             |

| Path 13    | 60       | 3      | 1      | 2           | count_reg_reg[15]/C | count_reg_reg[15]/D | 0.590       | 0.345       | 0.245     | -90         |             |

| Path 14    | 80       | 3      | 1      | 2           | count_reg_reg[19]/C | count_reg_reg[19]/D | 0.590       | 0.345       | 0.245     | -90         |             |

| Path 15    |          | 3      | 1      | 2           | count_reg_reg[23]/C | count_reg_reg[23]/D | 0.590       | 0.345       | 0.245     | -98         |             |

| Path 16    | 00       | 3      | 1      | 2           | count_reg_reg[27]/C | count_reg_reg[27]/D | 0.590       | 0.345       | 0.245     | -98         |             |

| Path 17    | 00       | 3      | 1      | 2           | count_reg_reg[31]/C | count_reg_reg[31]/D | 0.590       | 0.345       | 0.245     | -00         |             |

| - Path 18  |          | 3      | 1      | 2           | count_reg_reg[3]/C  | count_reg_reg[3]/D  | 0.590       | 0.345       | 0.245     | -10         |             |

| L Path 19  | 00       | 3      | 1      | 2           | count_reg_reg[0]/C  | count_reg_reg[0]/D  | 0.599       | 0.349       | 0.250     | -00         |             |

| Path 20    | 60       | 3      | 1      | 2           | count_reg_reg[12]/C | count_reg_reg1121/D | 0.599       | 0.349       | 0.250     | -00         |             |

Figure 6.9 Proposed Hold Delay for N=32

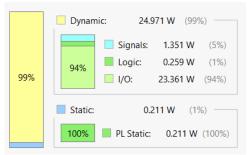

Figure 6.10 shows proposed power measurements for N=32. Here, the total power is 25.182 W, Static power includes PL Static power of 0.211 W, Dynamic power includes signal power of 1.351 W, Logic power of 0.259 W and I/O power of 23.361 W

Figure 6.10 Proposed power for N=32

#### 6.3 Existing Shift Register

Figure 6.11 Existing Shift Register Result for N=32

Figure 6.12 shows existing area measurements for N=32. Here, 540 number of LUT's are used out of Available 133800 LUT's which consumes 0.40% of utilization, 28 number of FF's are used out of Available 267600 FF's which consumes 0.01% of utilization, 3 number of DSP's are used out of Available 740 DSP's which consumes 0.41% of utilization, 68 number of IO's are used out of Available 500 IO's which consumes 13.60% of utilization, 1 number of BUFG's are used out of Available 32 BUFG's which consumes 3.13% of utilization.

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 540         | 133800    | 0.40          |

| FF       | 28          | 267600    | 0.01          |

| DSP      | 3           | 740       | 0.41          |

| Ю        | 68          | 500       | 13.60         |

| BUFG     | 1           | 32        | 3.13          |

Figure 6.12 Existing Area for N=32

Figure 6.13 shows existing Setup delay for N=32. Here, maximum Total Delay is 104.452 ns, maximum Logic Delay is 51.841 ns, maximum Net Delay is 52.610 ns.

| Name     | Slack ^1 | Levels | Routes | High Fanout | From       | То                 | Total Delay | Logic Delay | Net Delay | Requirement | Source Clock     |

|----------|----------|--------|--------|-------------|------------|--------------------|-------------|-------------|-----------|-------------|------------------|

| 🍹 Path 1 | 60       | 162    | 132    | 60          | data_in[0] | shift_reg_reg[0]/D | 104.452     | 51.841      | 52.610    | 60          | input port clock |

| 🕨 Path 2 | 80       | 153    | 124    | 60          | data_in[0] | shift_reg_reg(1)/D | 101.187     | 49.979      | 51.208    | 00          | input port clock |

| 🕨 Path 3 | 60       | 144    | 116    | 60          | data_in[0] | shift_reg_reg(2)/D | 96.760      | 47.901      | 48.858    | 60          | input port clock |

| Path 4   |          | 135    | 108    | 60          | data_in[0] | shift_reg_reg[3]/D | 92.717      | 46.049      | 46.667    | 00          | input port clock |

| 🕨 Path 5 | 00       | 127    | 101    | 57          | data_in[0] | shift_reg_reg[4]/D | 88.879      | 44.411      | 44.468    |             | input port clock |

| - Path 6 | 60       | 119    | 94     | 55          | data_in[0] | shift_reg_reg[5]/D | 85.508      | 42.445      | 43.063    | 60          | input port clock |

| 🕨 Path 7 | 80       | 111    | 87     | 53          | data_in[0] | shift_reg_reg[6]/D | 81.818      | 40.508      | 41.309    | 00          | input port clock |

| 🔓 Path 8 | 60       | 103    | 80     | 52          | data_in[0] | shift_reg_reg[7]/D | 78.311      | 38.595      | 39.716    | 60          | input port clock |

| 🕨 Path 9 | 80       | 96     | 74     | 49          | data_in[0] | shift_reg_reg[8]/D | 72.735      | 37.087      | 35.648    | 00          | input port clock |

| Path 10  | 60       | 89     | 68     | 47          | data_in[0] | shift_reg_reg[9]/D | 69.543      | 35,231      | 34,312    | 60          | input port clock |

Figure 6.13 Existing Setup Delay for N=32

Figure 6.14 shows existing Hold delay for N=32. Here, maximum Total Delay is 1.254 ns, maximum Logic Delay is 0.531 ns, maximum Net Delay is 0.772 ns.

| Name       | Slack ^1 | Levels | Routes | High Fanout | From        | То                    | Total Delay | Logic Delay | Net Delay | Requirement | Source Clock     |

|------------|----------|--------|--------|-------------|-------------|-----------------------|-------------|-------------|-----------|-------------|------------------|

| Path 11    | 60       | 1      | 1      | 28          | reset       | shift_reg_reg[18]/CLR | 0.979       | 0.482       | 0.497     | -00         | input port clock |

| 14 Path 12 | 00       | 1      | 1      | 28          | reset       | shift_reg_reg[19]/CLR | 0.979       | 0.482       | 0.497     | -00         | input port clock |

| 🕨 Path 13  | 60       | 2      | 1      | 28          | shift_right | shift_reg_reg[18]/D   | 1.049       | 0.530       | 0.519     | -60         | input port clock |

| Path 14    | 60       | 2      | 1      | 28          | shift_right | shift_reg_reg[19]/D   | 1.049       | 0.530       | 0.519     | -00         | input port clock |

| 🕨 Path 15  | 60       | 1      | 1      | 28          | reset       | shift_reg_reg[20]/CLR | 1.052       | 0.482       | 0.570     | -00         | input port clock |

| Path 16    | 60       | 1      | 1      | 28          | reset       | shift_reg_reg[21]/CLR | 1.052       | 0.482       | 0.570     | -60         | input port cloci |

| Path 17    | 00       | 2      | 1      | 28          | shift_right | shift_reg_reg[20]/D   | 1.220       | 0.530       | 0.690     | -00         | input port cloc  |

| Path 18    | 60       | 2      | 1      | 28          | shift_right | shift_reg_reg[21]/D   | 1.221       | 0.531       | 0.690     | -60         | input port clock |

| - Path 19  | 60       | 1      | 1      | 28          | reset       | shift_reg_reg[26]/CLR | 1.254       | 0.482       | 0.772     | -00         | input port clock |

| 1 Path 20  | 60       | 1      | 1      | 28          | reset       | shift reg reg[27]/CLR | 1.254       | 0.482       | 0.772     | -00         | input port clock |

#### Figure 6.14 Existing Hold Delay for N=32

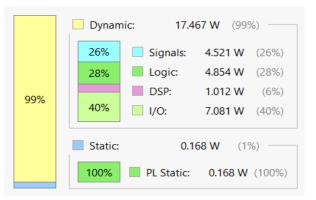

Figure 6.15 shows existing power measurements for N=32. Here, the total power is 17.635 W, Static power includes PL Static power of 0.168 W, Dynamic power includes signals power of 4.521 W, Logic power of 4.854 W, DSP power of 1.012 W and I/O power of 7.081 W.

#### Figure 6.15 Existing power for N=32

#### 6.4 Proposed Shift Register

Figure 6.16 Proposed Simulation Result for N=32

Figure 6.17 shows proposed area measurements for N=32. Here, 33 number of LUT's are used out of Available 133800 LUT's which consumes 0.02% of utilization, 32 number of FF's are used out of Available 267600 FF's which consumes 0.01% of utilization, 70 number of IO's are used out of Available 500 IO's which consumes 14.00% of utilization, 1 number of BUFG's are used out of Available 32 BUFG's which consumes 3.13% of utilization.

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 33          | 133800    | 0.02          |

| FF       | 32          | 267600    | 0.01          |

| ю        | 70          | 500       | 14.00         |

| BUFG     | 1           | 32        | 3.13          |

# Figure 6.17 Existing Area for N=32

Figure 6.18 shows proposed Setup delay for N=32. Here, maximum Total Delay is 6.599 ns, maximum Logic Delay is 3.380 ns, maximum Net Delay is 5.381 ns.

| Name    | Slack ^ | Levels | Routes | High Fanout | From                     | То                       | Total Delay | Logic Delay | Net Delay | Requirement | Source Clock     |

|---------|---------|--------|--------|-------------|--------------------------|--------------------------|-------------|-------------|-----------|-------------|------------------|

| Path 1  | 66      | 2      | 1      | 1           | data_in(17)              | next_shift_reg_reg[17]/D | 6.599       | 1.218       | 5.381     | 00          | input port cloc  |

| Path 2  |         | 2      | 1      | 1           | data_in(16)              | next_shift_reg_reg[16]/D | 6.589       | 1.219       | 5.371     | 00          | input port cloci |

| Path 3  | 00      | 2      | 1      | 1           | data_in(4)               | next_shift_reg_reg[4]/D  | 6.438       | 1.162       | 5.276     | 00          | input port clock |

| Path 4  |         | 2      | 1      | 1           | data_in(0)               | next_shift_reg_reg[0]/D  | 6.434       | 1.177       | 5.257     | 00          | input part clock |

| Path 5  | 00      | 2      | 1      | 1           | data_in(6)               | next_shift_reg_reg[6]/D  | 6.428       | 1.182       | 5.246     | 00          | input port clock |

| Path 6  |         | 2      | 1      | 1           | data_in(8)               | next_shift_reg_reg[8]/D  | 6.426       | 1.180       | 5.246     |             | input port clock |

| Path 7  |         | 2      | 1      | 1           | data_in(11)              | next_shift_reg_reg[11]/D | 6.403       | 1.169       | 5.233     |             | input port clock |

| Path 8  |         | 2      | 1      | 3           | next_shift_reg_reg[31]/C | shift_reg[31]            | 6.360       | 3.380       | 2.980     |             |                  |

| Path 9  |         | 2      | 1      | 1           | data_in(9)               | next_shift_reg_reg[9]/D  | 6.325       | 1.187       | 5.138     |             | input port cloci |

| Path 10 | -       | 2      | 1      | 1           | data_in[7]               | next shift reg reg171/D  | 6.281       | 1,182       | 5,100     |             | input part clock |

#### Figure 6.18 Proposed Setup Delay for N=32

Figure 6.19 shows proposed Hold delay for N=32. Here, maximum Total Delay is 0.454 ns, maximum Logic Delay is 0.255 ns, maximum Net Delay is 0.199 ns.

| Name      | Slack ^ | Levels | Routes | High Fanout | From                     | To                       | Total Delay | Logic Delay | Net Delay | Requirement | Source Cloc |

|-----------|---------|--------|--------|-------------|--------------------------|--------------------------|-------------|-------------|-----------|-------------|-------------|

| 🔓 Path 11 |         | 2      | 1      | 3           | next_shift_reg_reg[4]/C  | next_shift_reg_reg[3]/D  | 0.405       | 0.255       | 0.150     | -00         |             |

| > Path 12 |         | 2      | 1      | 3           | next_shift_reg_reg[13]/C | next_shift_reg_reg(12)/D | 0.415       | 0.255       | 0.160     | -00         |             |

| Path 13   |         | 2      | 1      | 3           | next_shift_reg_reg(8)/C  | next_shift_reg_reg[7]/D  | 0.420       | 0.255       | 0.165     | -07         |             |

| 🔓 Path 14 |         | 2      | 1      | 3           | next_shift_reg_reg[12]/C | next_shift_reg_reg(11)/D | 0.420       | 0.255       | 0.165     | -08         |             |

| 🍹 Path 15 | 00      | 2      | 1      | 3           | next_shift_reg_reg[10]/C | next_shift_reg_reg(9)/D  | 0.421       | 0.255       | 0.166     | -05         |             |

| 🖌 Path 16 | 60      | 2      | 1      | 3           | next_shift_reg_reg[18]/C | next_shift_reg_reg[17]/D | 0.423       | 0.255       | 0.168     | -00         |             |

| - Path 17 | 60      | 2      | 1      | 3           | next_shift_reg_reg[26]/C | next_shift_reg_reg(25)/D | 0.428       | 0.255       | 0.173     | -60         |             |

| 🖌 Path 18 |         | 2      | 1      | 3           | next_shift_reg_reg[7]/C  | next_shift_reg_reg(6)/D  | 0.431       | 0.255       | 0.176     | -00         |             |

| - Path 19 | 1/2     | 2      | 1      | 3           | next_shift_reg_reg[29]/C | next_shift_reg_reg[28]/D | 0.431       | 0.255       | D.176     |             |             |

| Path 20   |         | 2      | 1      | 3           | next shift reg reg[221/C | next shift reg.reg[23]/D | 0.454       | 0.255       | 0.199     |             |             |

Figure 6.19 Proposed Hold Delay for N=32

Figure 6.20 shows proposed power measurements for N=32. Here, the total power is 6.192 W, Static power includes PL Static power of 0.131 W, Dynamic power includes signal power of 0.521 W, Logic power of 0.099 W and I/O power of 5.441 W.

Figure 6.20 Proposed power for N=32

# **5. CONCLUSION**

In designing reconfigurable logic block-based sequential circuits, we have significantly reduced the number of lookup tables, leading to improvements in area, power consumption, and delay. Our proposed counter uses only 32 lookup tables, compared to 1286 in the existing design, cutting power usage to 25% and reducing delay. Similarly, our shift register design requires just 33 lookup tables, a major reduction from 540, and consumes only 6% of the power, with lower delay. These innovations result in more efficient and high-performance counters and shift registers.

# REFERENCES

- Sanadhya, Minakshi, and Devendra Kumar Sharma. "Study of Adiabatic Logic-Based Combinational and Sequential Circuits for Low-Power Applications." In Low Power Architectures for IoT Applications, pp. 47-84. Singapore: Springer Nature Singapore, 2023.

- Govindaraj.V, S. Dhanasekar, K. Martinsagayam, Digvijay Pandey, Binay Kumar Pandey, and Vinay Kumar Nassa.

"Low-power test pattern generator using modified LFSR." Aerospace Systems (2023): 1-8.

- [3] Pomeranz, "Testability Evaluation for Local Design Modifications." IEEE Transactions on Very Large-Scale Integration (VLSI) Systems (2023).

- [4] Angadi, Aditi, Shreya Umarani, Totashri Sajjanar, Rakshita Karnam, Kotresh Marali, and Shrikanth Shirakol.

"Architectural Design of Built in Self-Test for VLSI Circuits

using LFSR." In 2023 International Conference on Applied Intelligence and Sustainable Computing (ICAISC), pp. 1-7. IEEE, 2023.

- [5] Chandra, B. Ravi, Chinta Pranitha, Aunupati Ediga Preethi, Konkala Pavani, Mantriki Rajini, and Houdekari Mounika Bai. "Implementation of Ripple Carry Adder Using Full Swing Gate Diffusion Input." In 2023 7th International Conference on Trends in Electronics and Informatics (ICOEI), pp. 44-50. IEEE, 2023.

- [6] Priyadarshini, V., M. Manaswini, M. Krishna Babu, and M. Mallika. "DESIGN OF LOW POWER AND HIGH-SPEED CMOS D-FLIPFLOP USING HYBRID LOW POWER TECHNIQUES."

- [7] Sanadhya, Minakshi, and Devendra Kumar Sharma. "D flipflop design by adiabatic technique for low power applications." Indonesian Journal of Electrical Engineering and Computer Science 29, no. 1 (2023): 141-146.

- [8] Shah, Owais Ahmad, Geeta Nijhawan, and Imran Ahmed Khan. "A glitch free variability resistant high speed and low power sense amplifier-based flip flop for digital sequential circuits." Engineering Research Express 5, no. 3 (2023): 035046.

- [9] Hu, Yinghua, Yuke Zhang, Kaixin Yang, Dake Chen, Peter A. Beerel, and Pierluigi Nuzzo. "On the Security of Sequential Logic Locking Against Oracle-Guided Attacks." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (2023).

- [10] Ramakrishnan, Kannan, and K. Vidhya. "Design and Optimization of Sequence Generator Using NN Transvidkan Gate." (2023).

- [11] Harikrishna, A., Chowdamjollu Sai Siddartha, Kokollu Venkatesh, Guduru Bose, and Burla Bhuvan Shyam Reddy.

"A LOW POWER BINARY SQUARE ROOTER USING REVERSIBLE LOGIC." Turkish Journal of Computer and Mathematics Education (TURCOMAT) 14, no. 2 (2023): 435-443.

- [12] NOUSHEEN, MD SANA, and T. VIJAY KUMAR. "IMPLEMENTATION OF LOSSLESS IMAGE COMPRESSION USING FUZZY BASED MODIFIED GOLOMB RICE ENCODING." Journal of Engineering Sciences 14, no. 02 (2023).

- [13] Geonhwi, Bomin Joo, and Bai-Sun Kong. "CMOS Clock-Gated Synchronous Up/Down Counter with High-Speed Local Clock Generation and Compact Toggle Flip-Flop." IEEE Transactions on Circuits and Systems I: Regular Papers (2023).

Volume 13 Issue 02 2025

- [14] Moraitis, Michail. "FPGA Bitstream Modification: Attacks and Countermeasures." IEEE Access 11 (2023): 127931-127955.

- [15] Irith. "Test Data Compression for Transparent-Scan Sequences." IEEE Transactions on Very Large-Scale Integration (VLSI) Systems 31, no. 4 (2023): 601-605.

- [16] Khan, Imran Ahmed, Owais Ahmad Shah, Amrita Rai, Puneet Sharma, Prakhar Mishra, and Satvik Vats. "Odd Counter: New Design and Performance Analysis using Carbon Nano Tube Transistors for High Performance Applications." In 2023 International Conference on Computational Intelligence and Sustainable Engineering Solutions (CISES), pp. 610-613. IEEE, 2023.

- [17] Kumar, Chaudhry Indra, Abhishek Chaudhary, and Shreyansh Upadhyaya. "Design of high-performance energy efficient CMOS voltage level shifter for mixed signal circuits applications." Integration (2023): 102133.

- [18] Veena, M. B., P. H. Pavan, Sneha Bhusaraddi, and Shruti Ashok Singanamalli. "4-BIT Linear Feedback Shift Register Counter In 45nm Technology Using Pass Transistor Logic." In 2023 International Conference on Advances in Electronics, Communication, Computing and Intelligent Information Systems (ICAECIS), pp. 298-302. IEEE, 2023.